강의 요약: EE542 Lecture 12 - Logic, Memory, and Reconfigurable Hardware Accelerators

이번 강의는 클라우드 컴퓨팅과 병렬 처리에서 사용되는 로직 연산, 메모리 기술, 그리고 **재구성 가능한 하드웨어 가속기(FPGA)**에 대한 심도 있는 내용을 다루었다. 디지털 로직부터 FPGA의 설계 및 응용까지 폭넓은 주제를 포함한다.

주요 내용

1. 디지털 로직의 기본

• AND, OR, NOT 연산:

• Boolean 대수의 기본 연산. AND, OR, NOT 게이트를 활용해 다양한 논리적 기능 구현.

• NAND, NOR, XOR, XNOR 연산:

• 복잡한 로직을 구현하는 기본 게이트.

• NAND와 NOR는 “범용 게이트”로 사용 가능.

• 카르노 맵 (Karnaugh Map):

• 로직 간소화에 사용되는 시각적 도구.

• 다중 입력 논리 회로의 최적화에 효과적.

2. 메모리 기술

• SRAM (Static RAM):

• 빠른 접근 속도와 안정성 제공.

• 주로 캐시에 사용.

• DRAM (Dynamic RAM):

• 높은 저장 밀도와 비용 효율성.

• 정기적으로 데이터 리프레시 필요.

• 마그네틱 디스크:

• 대규모 데이터 저장, 하지만 속도가 느림.

• 데이터 래치(D-Latch):

• 데이터 저장과 동기화에 사용.

3. FPGA (Field Programmable Gate Array)

• 특징:

• 재구성이 가능한 하드웨어로, 비용 효율적이고 유연함.

• 프로토타이핑과 연구, 교육에 적합.

• FPGA 설계 도구:

• 하드웨어와 소프트웨어의 협력 설계(Co-design).

• 제한적인 프로그래밍 환경과 하드웨어 자원 최적화 필요.

• 응용 사례:

• 데이터 암호화, 네트워크 처리, 머신러닝 가속.

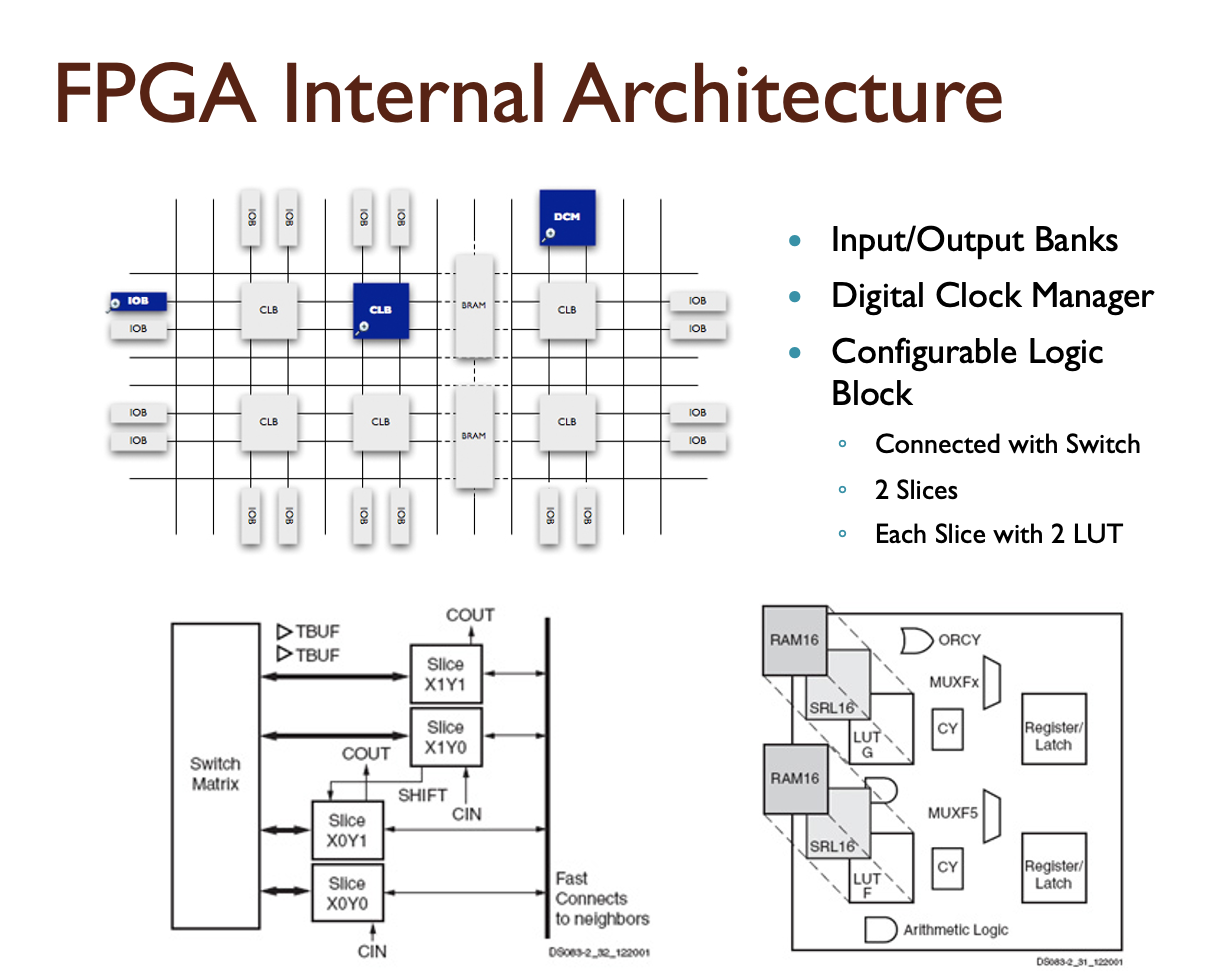

4. FPGA 아키텍처

• 구조적 특징:

• Configurable Logic Blocks(CLB): 프로그램 가능한 논리 블록.

• Digital Clock Manager: 타이밍 제어.

• LUT(Lookup Table): 논리 연산을 저장하고 수행.

• SoC(System on Chip):

• 임베디드 메모리와 프로세서를 통합.

• 고속 네트워크 I/O와 암호화 기능 제공.

5. FPGA의 장점과 단점

• 장점:

• 프로그래밍 가능성과 높은 유연성.

• ASIC 대비 설계 및 테스트 비용 절감.

• 단점:

• 프로그래밍 환경의 복잡성.

• 하드웨어 자원 사용 최적화 필요.

6. 응용과 도전

• 하드웨어-소프트웨어 협업 설계:

• FPGA와 소프트웨어 간의 통합이 여전히 어렵지만, 점진적으로 개선되고 있음.

• 사용 사례:

• 머신러닝 가속기, 데이터 분석, IoT 장치.

요약

이 강의는 디지털 로직과 메모리 기술, FPGA와 같은 하드웨어 가속기의 원리와 응용을 설명한다. FPGA는 높은 성능과 유연성을 제공하며, 클라우드 컴퓨팅과 고성능 컴퓨팅의 핵심 기술로 자리 잡고 있다.

'Learn > '24_Fall_(EE542) Internet&Cloud Computin' 카테고리의 다른 글

| (Lecture 15) IIoT Real World Example (0) | 2025.01.09 |

|---|---|

| (Lecture 13) Network with RDMA (0) | 2025.01.08 |

| (Lecture 11) Hardware Acceleration in Cloud (0) | 2025.01.08 |

| (Lecture 10) Uses of Cloud (0) | 2025.01.08 |

| (Lecture 9) Cloud Computing (1) | 2025.01.08 |